Tutorial – Introduction to VHDL

VHDL is a horrible acronym. It stands for VHSIC Hardware Description Language. An acronym inside an acronym, awesome! VHSIC stands for Very High Speed Integrated Circuit. Therefore, VHDL expanded is Very High Speed Integrated Circuit Hardware Description Language. PHEW that’s a mouthful. VHDL is one of the two languages used by education and business to design FPGAs and ASICs. You might first benefit from an introduction to FPGAs and ASICs if you are unfamiliar with these fascinating pieces of circuitry. VHDL and Verilog are the two languages digital designers use to describe their circuits, and they are different by design than your traditional software languages such as C and Java.

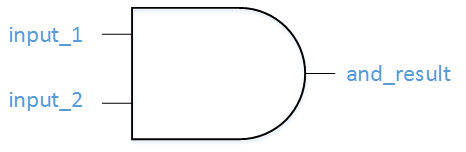

For the example below, we will be creating a VHDL file that describes an And Gate. As a refresher, a simple And Gate has two inputs and one output. The output is equal to 1 only when both of the inputs are equal to 1. Below is a picture of the And Gate that we will be describing with VHDL.

Let’s get to it! The fundamental unit of VHDL is called a signal. For now let’s assume that a signal can be either a 0 or a 1 (there are actually other possibilities, but we will get to that). Here is some basic VHDL logic:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

The first line of code defines a signal of type std_logic and it is called and_gate. Std_logic is the type that is most commonly used to define signals, but there are others that you will learn about. This code will generate an AND gate with a single output (and_gate) and 2 inputs (input_1 and input_2). The keyword “and” is reserved in VHDL. The <= operator is known as the assignment operator. When you verbally parse the code above, you can say out loud, “The signal and_gate GETS input_1 and-ed with input_2.”

Now you may be asking yourself where input_1 and input_2 come from. Well as their name implies they are inputs to this file, so you need to tell the tools about them. Inputs and outputs to a file are defined in an entity. An entity contains a port that defines all inputs and outputs to a file. Let’s create a simple entity:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

This is your basic entity. It defines an entity called example_and and 3 signals, 2 inputs and 1 output, all of which are of type std_logic. One other VHDL keyword is needed to make this complete and that is architecture. An architecture is used to describe the functionality of a particular entity. Think of it a thesis paper: the entity is the table of contents and the architecture is the content. Let’s create an architecture for this entity:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

The above code defines an architecture called rtl of entity example_and. All signals that are used by the architecture must be defined between the “is” and the “begin” keywords. The actual architecture logic comes between the “begin” and the “end” keywords. You’re almost done with this file. One last thing you need to tell the tools is which library to use. A library defines how certain keywords behave in your file. For now, just take it for granted that you need to have these 2 lines at the top of your file:

library ieee; use ieee.std_logic_1164.all;

Congratulations! You have created your first VHDL file. You can see the completed file here:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Does it seem like you had to write a lot of code just to create a stupid and gate? First of all, and gates aren’t stupid. Secondly, you are correct; VHDL is a very verbose language. Get used to the fact that doing something that was very easy in software will take you significantly longer in an HDL such as Verilog or VHDL. But just ask some software guy to try to generate an image to a VGA monitor that displays Conway’s Game of Life and watch their head spin in amazement! By the way, that video is created with VHDL and an FPGA. You will be able to do that soon enough!

Next we will discuss another fundamental VHDL keyword: process.

Thanks. This was a very helpful example for someone in another continent trying to figure out how to get a professor’s whiteboard drawings of circuits accessible to a blind student. They asked me because of this. https://research.library.kutztown.edu/cisfaculty/5/

Hi Russell,

I’ve been trying to use your website for some weeks now, but there’s a google ad banner that covers the content. Could you please do something about this? It’s practically impossible to do anything and to be honest, I’d have used another website if I didn’t have a go board.

Thank you.

I’ve turned off auto-ads on the site. Please let me know if this problem still exists!

Trafford?

Great content and great website? Say did you build the site yourself?

Why did we use signal and_gate : std_logic;?

Couldn’t we just use the following directly?

architecture rtl of example_and is

begin

and_result <= input_1 and input_2;

end rtl;

Yes, that works well, but using `signal` is just showing how we can break it down into steps, and introduces a concept important for later use as well.

That was so nicely explained! Very simple and straight to the point! Thanks 😉